# JEDEC STANDARD

# **Ball Grid Array Pinouts Standardized for 32-Bit Logic Functions**

# **JESD75**

**NOVEMBER 1999**

ELECTRONIC INDUSTRIES ALLIANCE

JEDEC Solid State Technology Association

### NOTICE

EIA/JEDEC standards and publications contain material that has been prepared, reviewed, and approved through the JEDEC Board of Directors level and subsequently reviewed and approved by the EIA General Counsel.

EIA/JEDEC standards and publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than JEDEC members, whether the standard is to be used either domestically or internationally.

EIA/JEDEC standards and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action JEDEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the EIA/JEDEC standards or publications.

The information included in EIA/JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer viewpoint. Within the JEDEC organization there are procedures whereby an EIA/JEDEC standard or publication may be further processed and ultimately become an ANSI/EIA standard.

No claims to be in conformance with this standard may be made unless all requirements stated in the standard are met.

Inquiries, comments, and suggestions relative to the content of this EIA/JEDEC standard or publication should be addressed to JEDEC Solid State Technology Association, 2500 Wilson Boulevard, Arlington, VA 22201-3834, (703)907-7560/7559 or www.jedec.org

Published by ©ELECTRONIC INDUSTRIES ALLIANCE 1999 2500 Wilson Boulevard Arlington, VA 22201-3834

This document may be downloaded free of charge, however EIA retains the copyright on this material. By downloading this file the individual agrees not to charge or resell the resulting material.

PRICE: Please refer to the current Catalog of JEDEC Engineering Standards and Publications or call Global Engineering Documents, USA and Canada (1-800-854-7179), International (303-397-7956)

> Printed in the U.S.A. All rights reserved

### PLEASE!

## DON"T VIOLATE THE LAW!

This document is copyrighted by the Electronic Industries Alliance and may not be reproduced without permission.

Organizations may obtain permission to reproduce a limited number of copies through entering into a license agreement. For information, contact:

JEDEC Solid State Technology Association 2500 Wilson Boulevard Arlington, Virginia 22201-3834 or call (703) 907-7559

#### BALL GRID ARRAY PINOUTS STANDARDIZED FOR 32-BIT LOGIC FUNCTIONS

# (Formerly JEDEC Board Ballot JCB-99-51, formulated under the cognizance of the JC-40 Committee on Digital Logic.)

#### **1 Background**

#### 1.1 Purpose

To provide a pinout standard for dual-die 32-bit logic devices offered in a 96- and 114-ball grid array package for uniformity, multiplicity of sources, elimination of confusion, ease of device specification, and ease of use.

#### 1.2 Scope

This standard defines device pinout for 32-bit wide buffer, driver and transceiver functions. This pinout specifically applies to the conversion of DIP-packaged 16-bit logic devices to LFBGA-packaged dual-die 32-bit logic devices.

#### 2 Definitions for the purpose of this document

#### 2.1 Definitions

DIP: Dual In-line Pin Package (gull-wing)

LFBGA:Low-Profile Fine-Pitch Ball Grid Array (MO-205)

SSOP: Shrink Small-Outline Package; 0.25" lead pitch; 0.3" wide body (MO-118)

TSSOP: Thin Shrink Small-Outline Package; 0.5-mm lead pitch; 6.4-mm wide body (MO-153)

TVSOP: Thin Very Small-Outline Package; 0.4-mm lead pitch; 4.4-mm wide body (MO-194)

#### **3** Pinout standard

#### 3.1 Description

The following criteria shall be used to convert existing 16-bit logic device functions offered in 48- and 56-pin DIP packages (SSOP, TSSOP, TVSOP) to 32-bit logic device functions offered in 96- and 114-ball LFBGA packages:

- A. Attributes for the LFBGA packages shall be as follows:

- (1) 96-Ball, 0.8-mm ball pitch with 5.5-mm × 13.5-mm body size and 6-row × 16-column ball matrix, or the

- (2) 114-Ball, 0.8-mm ball pitch with 5.5-mm × 16.0-mm body size and 6-row × 19-column ball matrix.

- B. Device conversion shall be as follows:

| DIP package | LFBGA package |

|-------------|---------------|

| 48-pin      | 96-ball       |

| 56-pin      | 114-ball      |

C. The pinout conversions shall be in accordance with the diagrams shown in section 3.3 and 3.6.

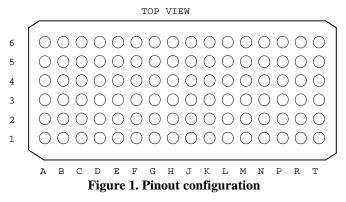

#### 3.2 96-ball LFBGA (MO-205CC)

### 3.3 Pin conversion for 96-ball LFBGA

The pin conversion adopts the naming convention of logic devices in 48-pin packages (e.g. SSOP, TSSOP, TVSOP).

| 6 | A46¶                              | A43¶            | A40¶             | A37¶             | A35¶             | A32¶             | A29¶            | A27¶             | B46¶             | B43¶            | B40 <sup>¶</sup> | B37 <sup>¶</sup> | B35 <sup>¶</sup> | B32 <sup>¶</sup> | B29¶             | B27 <sup>¶</sup> |

|---|-----------------------------------|-----------------|------------------|------------------|------------------|------------------|-----------------|------------------|------------------|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 5 | A47¶                              | A44¶            | A41¶             | A38¶             | A36¶             | A33¶             | A30¶            | A26¶             | B47 <sup>¶</sup> | B44¶            | B41 <sup>¶</sup> | B38 <sup>¶</sup> | B36¶             | B33 <sup>¶</sup> | B30 <sup>¶</sup> | B26 <sup>¶</sup> |

| 4 | A48 <sup>§</sup>                  | $A45^{\dagger}$ | A42 <sup>‡</sup> | A39 <sup>†</sup> | A34 <sup>†</sup> | A31 <sup>‡</sup> | $A28^{\dagger}$ | A25 <sup>§</sup> | B48 <sup>§</sup> | $B45^{\dagger}$ | B42 <sup>‡</sup> | $B39^{\dagger}$  | $B34^{\dagger}$  | B31 <sup>‡</sup> | $B28^{\dagger}$  | B25 <sup>§</sup> |

| 3 | A1 <sup>§</sup>                   | $A4^{\dagger}$  | A7 <sup>‡</sup>  | $A10^{\dagger}$  | $A15^{\dagger}$  | A18 <sup>‡</sup> | $A21^{\dagger}$ | A24 <sup>§</sup> | B1 <sup>§</sup>  | $B4^{\dagger}$  | B7 <sup>‡</sup>  | $B10^{\dagger}$  | $B15^{\dagger}$  | B18 <sup>‡</sup> | B21 <sup>†</sup> | B24 <sup>§</sup> |

| 2 | A2 <sup>¶</sup>                   | A5¶             | A8¶              | A11¶             | A13¶             | A16¶             | A19¶            | A23¶             | B2 <sup>¶</sup>  | B5¶             | B8¶              | B11¶             | B13¶             | B16 <sup>¶</sup> | B19¶             | B23 <sup>¶</sup> |

| 1 | A3¶                               | A6¶             | A9¶              | A12¶             | A14¶             | A17¶             | A20¶            | A22¶             | B3¶              | B6 <sup>¶</sup> | B9¶              | B12 <sup>¶</sup> | B14 <sup>¶</sup> | B17 <sup>¶</sup> | B20 <sup>¶</sup> | B22 <sup>¶</sup> |

|   | А                                 | В               | С                | D                | Е                | F                | G               | Н                | J                | K               | L                | М                | Ν                | Р                | R                | Т                |

|   | Figure 2. Pin conversion top view |                 |                  |                  |                  |                  |                 |                  |                  |                 |                  |                  |                  |                  |                  |                  |

#### 3.4 Pin assignment for 96-ball LFBGA

<sup>†</sup>GND: B3, B4, D3, D4, E3, E4, G3, G4, K3, K4, M3, M4, N3, N4, R3, and R4

<sup>‡</sup>V<sub>DD</sub>: C3, C4, F3, F4, L3, L4, P3, and P4

<sup>§</sup>Control: A3, A4, H3, H4, J3, J4, T3, and T4

<sup>¶</sup>I/O and Signals: all Row-1, -2, -5 and -6 pins.

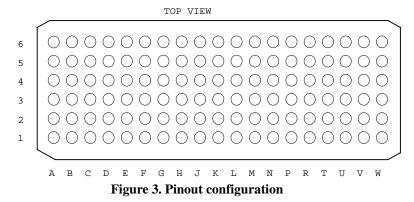

#### 3.5 114-ball LFBGA (MO-205DC)

#### 3.6 3.6 Pin conversion for 114-ball LFBGA

The pin conversion adopts the naming convention of logic devices in 56-pin packages (e.g. SSOP, TSSOP, TVSOP).

| 6 | A52#             | A49 <sup>#</sup> | A47 <sup>#</sup> | A44 <sup>#</sup> | A42 <sup>#</sup> | A40 <sup>#</sup> | A37 <sup>#</sup> | A36 <sup>#</sup> | A33 <sup>#</sup> | $\mathrm{NC}^*$  | B52 <sup>#</sup>                  | B49 <sup>#</sup> | B47 <sup>#</sup> | B44 <sup>#</sup>       | B42 <sup>#</sup> | B40 <sup>#</sup> | B37 <sup>#</sup> | B36 <sup>#</sup> | B33 <sup>#</sup> |  |  |  |  |

|---|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-----------------------------------|------------------|------------------|------------------------|------------------|------------------|------------------|------------------|------------------|--|--|--|--|

| 5 | A54 <sup>§</sup> | A51#             | A48#             | A45#             | A43#             | A41#             | A38#             | A34#             | A31 <sup>§</sup> | B55 <sup>§</sup> | B54 <sup>§</sup>                  | B51 <sup>#</sup> | B48 <sup>#</sup> | B45 <sup>#</sup>       | B43#             | B41#             | B38 <sup>#</sup> | B34 <sup>#</sup> | B31 <sup>§</sup> |  |  |  |  |

| 4 | A55§             | A56¶             | $A53^{\dagger}$  | A50 <sup>‡</sup> | $A46^{\dagger}$  | A39 <sup>†</sup> | A35 <sup>‡</sup> | $A32^{\dagger}$  | A30 <sup>§</sup> | A29¶             | B56¶                              | $B53^{\dagger}$  | B50 <sup>‡</sup> | $\mathrm{B46}^\dagger$ | B39 <sup>†</sup> | B35 <sup>‡</sup> | $B32^{\dagger}$  | B30 <sup>§</sup> | B29¶             |  |  |  |  |

| 3 | A2§              | A1 <sup>§</sup>  | $A4^{\dagger}$   | A7 <sup>‡</sup>  | $A11^{\dagger}$  | $A18^{\dagger}$  | A22 <sup>‡</sup> | $A25^{\dagger}$  | A27§             | A28§             | B1§                               | $B4^{\dagger}$   | B7 <sup>‡</sup>  | $B11^{\dagger}$        | $B18^{\dagger}$  | B22 <sup>‡</sup> | $B25^{\dagger}$  | B27 <sup>§</sup> | B28 <sup>§</sup> |  |  |  |  |

| 2 | A3§              | A6 <sup>#</sup>  | A9#              | A12#             | A14#             | A16 <sup>#</sup> | A19 <sup>#</sup> | A23#             | A26 <sup>§</sup> | B2§              | B3§                               | B6 <sup>#</sup>  | B9 <sup>#</sup>  | B12#                   | B14 <sup>#</sup> | B16 <sup>#</sup> | B19 <sup>#</sup> | B23 <sup>#</sup> | B26 <sup>§</sup> |  |  |  |  |

| 1 | A5#              | A8#              | A10 <sup>#</sup> | A13 <sup>#</sup> | A15 <sup>#</sup> | A17 <sup>#</sup> | A20 <sup>#</sup> | A21#             | A24#             | $NC^*$           | B5 <sup>#</sup>                   | B8 <sup>#</sup>  | B10 <sup>#</sup> | B13 <sup>#</sup>       | B15 <sup>#</sup> | B17 <sup>#</sup> | B20 <sup>#</sup> | B21 <sup>#</sup> | B24 <sup>#</sup> |  |  |  |  |

|   | А                | В                | С                | D                | Е                | F                | G                | Н                | J                | Κ                | L                                 | М                | Ν                | Р                      | R                | Т                | U                | V                | W                |  |  |  |  |

|   |                  |                  |                  |                  |                  | F                | ligure           | e 4. Pi          | in con           | nversi           | Figure 4. Pin conversion top view |                  |                  |                        |                  |                  |                  |                  |                  |  |  |  |  |

<sup>†</sup>GND Pins: C3, C4, E3, E4, F3, F4, H3, H4, M3, M4, P3, P4, R3, R4, U3, and U4

<sup>‡</sup>V<sub>DD</sub> Pins: D3, D4, G3, G4, N3, N4, T3, and T4

<sup>§</sup>Control Pins: A2, A3, A4, A5, B3, J2, J3, J4, J5, K2, K3, K5, L2, L3, L5, V3, V4, W2, W3, and W5

<sup>¶</sup>GND or Control Pins: B4, K4, L4, and W4

<sup>#</sup>I/O Pins: A1, A6, B1, B2, B5, B6, C1, C2, C5, C6, D1, D2, D5, D6, E1, E2, E5, E6, F1, F2, F5, F6, G1, G2, G5, G6, H1, H2, H5, H6, J1, J6, L1, L6, M1, M2, M5, M6, N1, N2, N5, N6, P1, P2, P5, P6, R1, R2, R5, R6, T1, T2, T5, T6, U1, U2, U5, U6, V1, V2, V5, V6, W1, and W6

<sup>\*</sup>No Connection Pins: K1 and K6

4 Reference to other applicable JEDEC standards and publications

JEP95: JEDEC Registered and Standard Outlines for Solid State and Related Products